我认为这个问题是为我量身定制的! 作为前Teradyne ATE工程师和现在的AMD DFT +数字IC设计工程师,我将以个人项目经验来谈论这个问题。

让我先谈谈完整的测试过程,然后再回答该主题的两个问题。

1.芯片测试概述

芯片测试分为两个阶段,一个阶段是CP(芯片探测)测试,另一个阶段是晶圆(Wafer)测试。 另一个是FT(最终测试)测试,即在封装芯片之后执行测试。

CP测试的目的是在包装之前筛选出不良芯片,以节省包装成本。 同时,可以更直接地知道晶片的产量。 CP测试可以检查晶圆厂的制造工艺水平。 现在,对于一般的晶圆成熟技术而言,许多公司节省了更多的CP,以降低CP测试的成本。 是否进行CP测试是综合考虑包装成本和CP测试成本的结果。

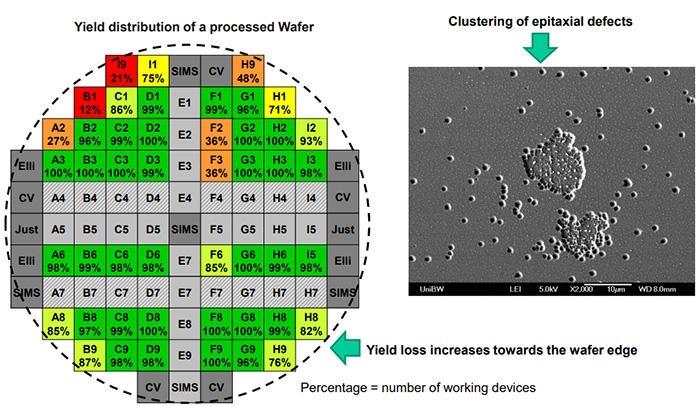

晶圆距离边缘越近,裸片的可能性越大(小正方形,即未封装的芯片)。

随着芯片尺寸越来越大,测试变得越来越复杂。 ATE(自动测试设备)应运而生。 目前,最大的ATE公司是Teradyne和研华。 NI目前正在这样做,许多小型公司正在使用NI仪器。 国内知名公司包括长川科技。

作为集成了许多高精度仪器的设备,ATE自然很昂贵。 一个Teradyne的高端Ultra Flex可以在上海购买几套套房!

2.芯片测试流程

在测试之前,当然必须有ATE设备,CP测试需要探针卡,FT测试需要负载板,Socckt等。让我们举个全家福。 左下方是负载板(也称为DUT板),左第二是探针卡。

然后,芯片设计公司提供设计规范和测试规范(数据表),以制定测试计划,开发测试程序并建立测试项目。

测试计划图:

常规测试通常包括以下测试项目:

直流参数测试

它主要包括以下测试。 连续性测试(也称为开放/短路测试)主要检查芯片的插针以及与机器的连接是否完整。 其余测试将检查直流电参数是否在一定范围内。

连续性测试

泄漏测试(IIL / IIH)

电源电流测试(IDDQ)

其他电流/电压测试(IOZL / IOZH,IOS,VOL / IOL,VOH / IOH)

LDO,DCDC电源测试。

下图是开路/短路测试原理的示意图。 DUT(被测设备)引脚与两个保护二极管相连。 根据二极管的单向传导和截止电压特性,汲取/吸收电流,然后对其进行测试。电压取决于其是否在设定极限内。

整个过程由ATE的PE(Pin Electronics)仪器完成。

- 数字功能测试

测试的这部分主要是运行测试向量(模式),该模式是由设计公司的DFT工程师通过ATPG(自动测试模式生成)工具生成的。

模式测试基本上是添加刺激,然后捕获输出,然后与期望值进行比较。

与功能测试相对应的是结构测试,包括扫描,边界扫描等。根据芯片制造过程中产生的缺陷和故障模型生成图案。 有关详情,请参见下文。

https://zhuanlan.zhihu.com/p/161185302

应用结构测试可以更好地提高覆盖率。

当然,有内置的自测(BIST)主要用于内存测试。

- 交流参数测试

主要是AC计时测试,包括计时检查,例如建立时间,保持时间,传播延迟等。

- ADC和DAC测试

它主要是数模/数模混合测试,用于检查ADC / DAC之后的信号是否符合预期。 这个地方涉及很多信号知识。 一般来说,它包括静态测试和动态测试。

静态测试–直方图方法(INL,DNL)

动态测试– SNR,THD,SINAD

除上述常规测试项目外,还可以根据不同的芯片类型进行不同的测试,例如RF测试和SerDes高速测试。 出液测试等

基本测试流程图如下:

所有测试项目都在ATE上执行,通常需要几秒钟到几十秒,因为ATE是根据机器时间支付的(HiSilicons很少,并且像Apple这样的本地公司一次购买了几十个单元) ,因此缩短测试时间变得尤为重要! 另外,在大规模生产和测试常规芯片中,有数百万或数千万的芯片。 每个芯片节省一秒钟。 总体而言,缩短的时间仍然很大。

测试执行完成后,ATE将输出一个数据日志以显示测试结果。 对于测试通过或失败测试项目的差异,还将对其进行分类(Bin),最后由Handler进行排序。

数据记录图:

以上是芯片的完整测试过程。 放置两张有关封装测试工厂/实验室的环境图片以进行芯片测试:

关于该主题的两个问题:

1.诸如BGA之类的封装不应多次焊接,那么如何开机和测试呢?

对于封装的芯片,通常不需要焊接测试。 它与ATE机器之间的连接是通过socckt和负载板进行的。

socckt是放置芯片的基础,如下所示:

对于不同尺寸和不同封装类型的芯片,Socckt也有所不同,并且有一些特殊的制造商可以这样做。

首先将芯片放入socckt,然后将socckt放在负载板上,然后将负载板放在机器上。 一些承重板很重,这对许多女同志来说有点难!

负载板支持多个socckt,我们称其为site。 原理图如下,总共有6个位置,可以同时测试6个芯片:

2.功能这么多,真的和编写软件一样吗?需要时间

首先让我解释一下,芯片的逻辑功能是由IC验证工程师完成的。 它是在磁带出库之前,并不依赖于测试。

芯片测试中的功能测试/结构测试将运行该图案,该图案将测试芯片在制造过程中是否存在缺陷,从而影响功能/性能。

因此,测试工程师需要关心的是运行模式。 如果它不运行,则可以向DFT工程师进行诊断。

在测试项目中编写测试项目时,无需一行一行地编写代码。 通常ATE机器的嵌入式软件都有一个提供测试项目的模板,只需填写参数即可。 此外,针对一些主要客户的成熟测试项目,将开发一些测试模板,并保留必要的参数接口,以便可以轻松地应用于其他芯片测试。

写在最后:

完整的芯片测试并非仅由芯片测试工程师完成,而是需要设计工程师,DFT工程师的支持,以及多种因素的结合,例如可靠的EDA工具和出色的硬件支持。

芯片测试是极其重要的部分,发现缺陷芯片越早越好。 芯片领域有十倍的规律。 从设计->制造->封装和测试->系统级应用程序,如果每晚发现一个链接,芯片公司的成本将增加十倍! ! !

因此,设计公司特别注意测试。 如果将具有功能缺陷的芯片出售给客户,则损失会非常惨重,不仅会造成经济补偿,还会损害声誉。 因此,芯片测试的成本越来越高!

在集成电路行业,您必须在各个方面都非常小心。 磁带输出的成本为数十万美元,而一天的ATE机器要花费数十万美元。 芯片的利润可能只有几美分。 这也是IC行业投资周期长,收益低的原因。 基本上,它在过去几年一直在亏损。 幸运的是,该国越来越重视芯片,希望国内IC的发展会越来越好。

以上,鼓励!

资料来源:知乎www.zhihu.com

作者:温戈

[Zhihu Daily]数千万用户的选择,成为朋友圈中的最新事物并分享大牛。单击下载

这个问题还有52个答案,请参阅全部。

进一步阅读:

芯片,半导体和集成电路有什么区别?

iPhone 12的5nm芯片功能是否强大?

。Source